Carbon Nanotube Transistors May Soon Give Waning Moore’s Law a Boost

Share

Carbon nanotubes (CNTs) have long been touted as a potential material to take us beyond the limits of faltering silicon chips, but they've proven tricky to manufacture. Now scientists have demonstrated a way to build CNT transistors in a commercial silicon fabrication plant.

Essentially CNTs are rolled-up sheets of the one-atom-thick wonder material graphene. They are excellent semiconductors and transport charge carriers very quickly, which has made them a promising option for replacing silicon, which is starting to hit fundamental physical limits.

Last year, a team led by engineers from MIT broke new ground with a 16-bit microprocessor made up of 15,000 CNT transistors that could execute a basic computer program. The project was part of a $61 million project funded by DARPA, but despite using industry-standard design processes the chip was still fabricated in a research lab rather than using industrial processes.

Now though, a team made up of many of the same researchers has developed a new process that makes it possible to produce CNT transistors in commercial chip manufacturing facilities using standard equipment. They successfully tested the new approach in two separate plants: a commercial silicon manufacturing facility run by Analog Devices and a high-volume semiconductor foundry run by SkyWater Technology.

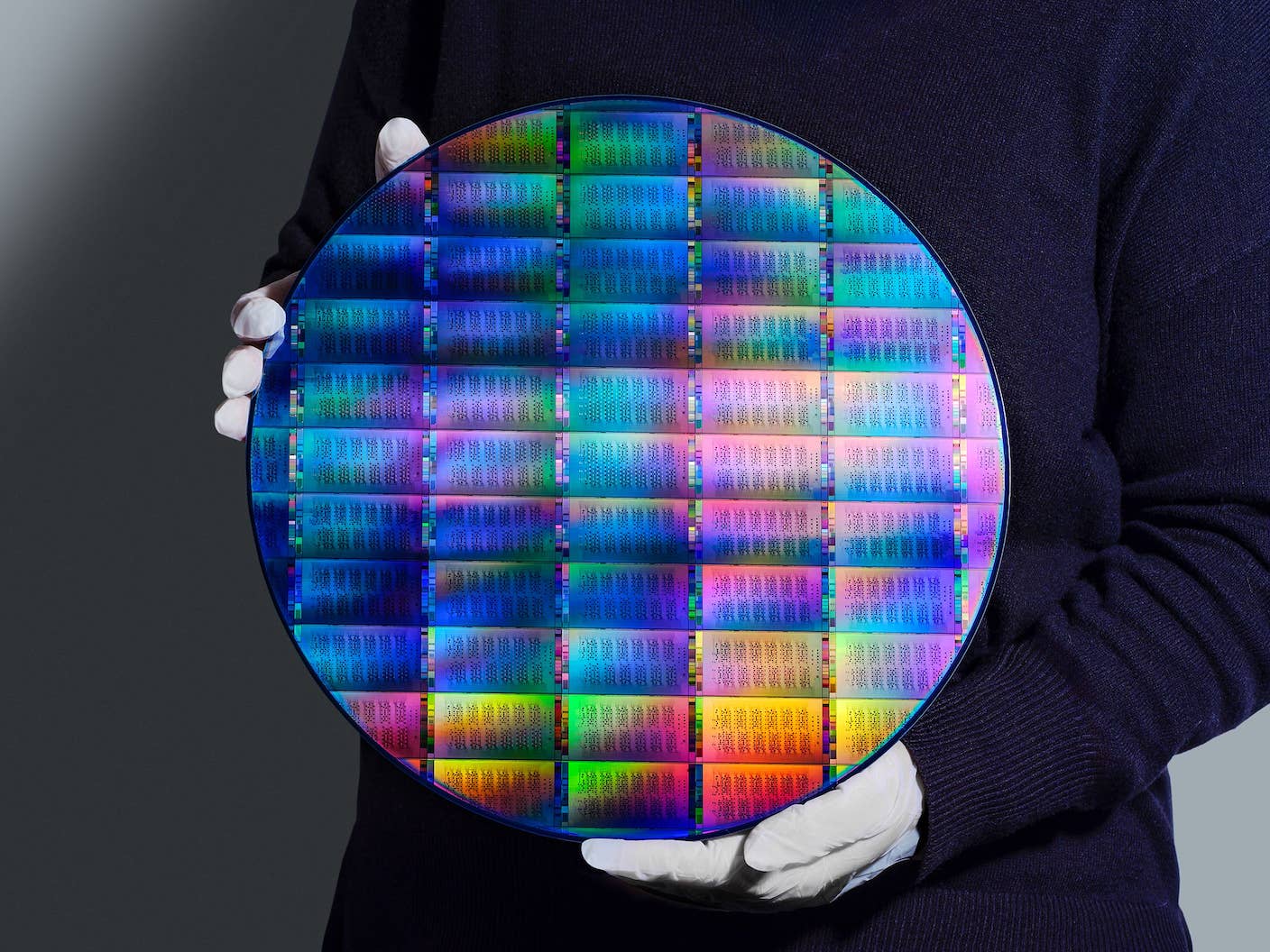

The team achieved this by tweaking one of the most popular approaches to creating CNT transistors, in which silicon wafers are dipped into a solution of CNTs. The problem with previous implementations of this approach is that it can take on the order of days for enough CNTs to get deposited on the wafer and requires highly-concentrated solutions, which are expensive and degrade quickly as the CNTs in the solution stick together faster.

So the researchers carried out a rigorous analysis of the process by which the CNTs get deposited on the wafer, detailed in a paper in Nature Electronics. They found that it involves a careful balancing act between the rates at which the CNTs stick to the wafer and the rate at which they come loose. Early on there are very few CNTs on the wafer, so the rate of deposition is very high, but as they build up the rate at which they escape again rises.

This results in the rate of deposition gradually plateauing until the two processes balance out and the number of CNTs stabilizes. If the wafer is then removed from the solution and dried, the deposited CNTs stay in place. This prompted the team to devise two new techniques that would slow the rate at which CNTs come loose and speed up the rate at which they get deposited.

While previous approaches relied on long soaks in the solution to ensure enough CNTs got deposited, the researchers instead carried out a series of 10-second soaks interspersed with drying. At each cycle the deposited CNTs are fixed in place, and the next dip has the same rapid deposition rate as a freshly-soaked wafer.

Be Part of the Future

Sign up to receive top stories about groundbreaking technologies and visionary thinkers from SingularityHub.

They also came up with another tactic where, instead of soaking the wafer in a solution, they applied a small amount of the solution on the surface of the wafer. The solvent in which the CNTs are dissolved then starts to evaporate, increasing the concentration of the solution and speeding up the deposition process.

Both these techniques can be run in parallel, and the researchers showed that they could speed up the CNT deposition process from 48 hours to just 150 seconds. This was achieved in commercial facilities and managed to uniformly distribute CNT transistors over an industry-standard 200 mm wafer.

There are some caveats. The output was not a working computer chip, merely a demonstration of the fabrication process, and the transistors had a gate length of 130nm, which is equivalent to chips released in 2001. The new process also only achieved a CNT density of about 45 CNTs per micrometer, which is still significantly below the optimum of 200 predicted by previous research.

However, the researchers also carried out an analysis of the relationship between CNT density and the energy efficiency of resulting chips and found that even at lower densities the savings can be significant. Even a density of 25 will result in a 2.5X boost in energy efficiency, compared to the 1.4X boost expected from shifting from today’s 7nm silicon process to the next-generation 5nm one.

While it is still a long road to converting this breakthrough into a working chip, it’s a significant step towards the future of high-performance CNT computing. Moore’s Law might get a shot in the arm just as it needs it the most.

Image Credit: Dean Simone from Pixabay

Related Articles

In the Scramble to Power AI, Investors Bet $140 Million on Data Centers at Sea

Quantum Computers Are Coming to Break Cryptography Faster Than Anyone Expected

Printed Neurons That Mimic Brain Cells Could Slash AI’s Energy Bill

What we’re reading